[Hamid\* et al., 7(4): April, 2018]

ICTM Value: 3.00

ISSN: 2277-9655 Impact Factor: 5.164 CODEN: IJESS7

# INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY

## COMPARATIVE ANALYSIS OF BOOTH'S MULTIPLIER IN TERMS OF DESIGN PARAMETER

Aamir Bin Hamid \*1, Nadeem Tariq Beigh 2, Shabeer Ahmad Ganiee3

\*School of Engineering, Sharda University, Greater Noida, UP, India \*2School of Engineering, Sharda University, Greater Noida, UP, India 3Department of Electronics & Communication, IUST, Pulwama, J&K, India

DOI: 10.5281/zenodo.1228673

#### **ABSTRACT**

In digital signal processing applications, one of the critical parameter in digital system design is performance. The IC's used in digital signal processing applications consume majority of IC power. Nearly 15 to 20 % of IC power is consumed by multiplication alone. A part from design, speed of operation and area are key requirement. In this paper different type of multipliers are compared in terms of design parameters. Booths multiplier offers several advantages over other type of multipliers in terms of area, power consumption and speed can further be improved using modified booths algorithm.

**KEYWORDS:** Array multiplier, Wallace tree multiplier, Vedic multiplier, booths multiplier

## I. INTRODUCTION

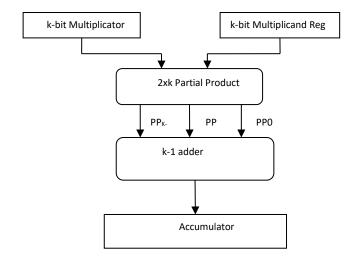

Multipliers play an integral part in modern electronics and other different types of applications. The need for low power VLSI system arises from two main reasons. Firstly, with the study growth of operating frequency and processing capacity per chip, large currents have to be delivered and the heat generated must be removed by proper cooling techniques. Secondly, battery life in portable electronic devices is limited and low power design directly leads to prolonged operation time. Extensive work is being carried out on low power multipliers at technological, physical, circuit and logic levels and as a result, several parallel multipliers are designed with different area-speed constraints. During the design of any device we need to keep in mind various parameters like speed of device, area of device, time consuming by device to performance this process, also regularity of the layout and power consumed by this device to perform this process. These all parameters are necessary to obtain the best processing design. For this we use various types of multipliers to perform process in VLSI implementation. As in a device we have to do lot of arithmetic processes like addition, subtraction and multiplications but among all multiplication is very important because the important path is found more by multipliers as it needs highest delay in all basic functional blocks in digital system [1]. Also it need lot of time as compared to other operation and also needs more hardware device. So to obtain better results in process we need to focus on multipliers because they help a lot in improvement of device performance. Various types of factors are there that help in making electronic design taking consideration of low power dissipation and faster speed. Nowadays many researchers have started working on multipliers design with high efficiency and the only purpose of it is to provided high speed and low power dissipation. This helps these multipliers well suited for different movable and difficult VLSI circuit implementations. In multipliers twin precision method is used to get dual output [2]. Multiplier architecture is divided into 3 parts: creation of partial product, summing of partial product and final addition. Block Diagram of multiplier architecture is shown in figure below. [3]

ISSN: 2277-9655 Impact Factor: 5.164 CODEN: IJESS7

Figure 1: Architecture of multiplier

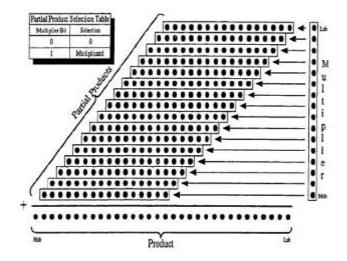

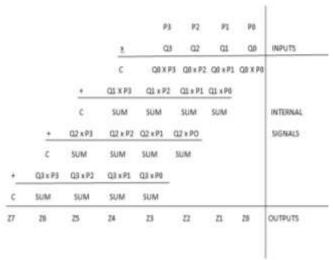

Digital multiplication does the process of addition of partial products in a particular order. Process by which addition of partial product array is done to provide the final result is the important distinctive reason between several multiplications. Figure below show how process is done on partial product array.

Figure 2: 16 bit partial product array

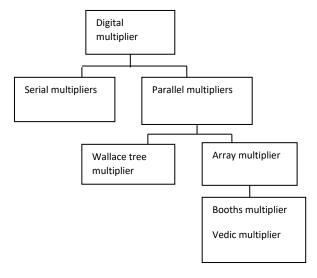

Different types of multipliers are there and these are classified as given below. Multipliers are classified on the basis of serial and parallel multipliers.

Figure 3: Digital multiplier classification

[Hamid\* et al., 7(4): April, 2018]

ICTM Value: 3.00

ISSN: 2277-9655 Impact Factor: 5.164 CODEN: IJESS7

Multiplication can be done using two multipliers like serial multipliers and parallel multipliers as shown below.

#### • Serial multiplier

Serial multiplier is the easy and simple type of multiplier but the process done is quit slow as the output we get in it is only after m clock cycles, where m is size of operands. Serial multipliers are considered only when the area and power is not necessary in device and also excess in delay is avoided.

#### • Parallel multiplier

Faster version of this serial multiplier can be achieved by adding partial products at single time. We can get this by unfolding the serial multiplier and achieve a combinational circuit in which there are several partial product generators mixed with several adders which perform in parallel. The multiplier which we get from that is called Parallel Multiplier and is shown in fig below

Figure 4. Serial type multiplier

Figure 5. Parallel type multiplier

### II. ARRAY MULTIPLIERS

Array multipliers are important because it has simple and regular layout of combinational circuit so process in it is simple. In this we use and gate to obtain partial product and we use  $m \times (m-2)$  full adders and m half

ISSN: 2277-9655 Impact Factor: 5.164 CODEN: IJESS7

adders. In this type of multiplier each of the product bit is fed to the full adder which add this product bit to the adder which we get previously and also to the carry of the least significant of the adder which we get before that. This process is done in rows and the length of multiplier is obtained by counting how many rows are used in this array multiplier also the thickness of multiplicand is achieved by thickness of each of the row of array multiplier. This type of multiplier is designed using following steps. Here the array multiplier of 16\*16 bit is simulated using Xilinx 8.1 tool [4]. The procedure of to design this multiplier is given below as step by step;

Here multiplier circuit is simply processed through add and shift algorithm. Partial product is obtained by the process of multiplication of the multiplicand with single multiplier bit. Then there is a process of shifting and their procedure is done according to bit order and after that it is added. Addition in this is done through very simple method using simple carry propagate adder. M-1 adders are needed where M denote length of the multiplier.

Figure 6: Structure of array multiplier

Algorithms used in are variables for multiplicand and multipliers, shift and add processes. But there are few demerits in array multiplier also as area is small in it also circuit complexity is also simple in it but it has some problems that it is low speed algorithm also power consumption is high in array multiplier[5]

## III. VEDIC MULTIPLIERS

Vedic multipliers play a vital role in multiplication process as there are large no of arithmetic operation in process and these operations are time consuming which decreases the speed of the multiplier. So to avoid this Vedic multipliers play an important role. It had become important method for quicker calculation and examination [11]. It is considered as the quickest and lower in terms of power as compared to array and booth multipliers [12]. This term has been obtained from Vedic mathematics which is anciently used in mathematics in India. As Vedic is treated as store house of information. [13]Vedic multiplier is composed of total 16 algorithms for various types of logic operations but among these algorithms vertically crossover method is considered most as it has lot of properties as compared to other 15 algorithms in terms of complexity as this algorithm is simple, better and is not complicated as compared to other algorithms[14]. Also speed of this algorithm is resourceful as compared to other 15 algorithms. Vertically crossover process is done by this way as shown below [15]. Let's take 2 numbers 30 and 27 how process is done in it is shown below:

30 X 27 = 810

3 0

2 7

Now we considered LSB of these two numbers and then multiply them with each other. After completion of process the result we get will become the LSB of the answer.

ISSN: 2277-9655 Impact Factor: 5.164 CODEN: IJESS7

Now in 2<sup>nd</sup> step we take these both numbers and then multiply them horizontally and then add these both together after that LSB of this output carried to the left of the first and the MSB bit is carried to the next step.

21 + 0 = 21

Now in final step we take MSB of these two numbers and then multiply these both numbers. Output of these two numbers are added by previous MSB of the process.

So from above example it is clear that Vedic multiplier is better as compared to array multiplier as the partial product is done in it parallel. So speed of this multiplier is considered as higher as compare to array multiplier.

#### IV. BOOTH'S MULTIPLIERS

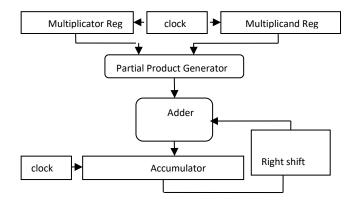

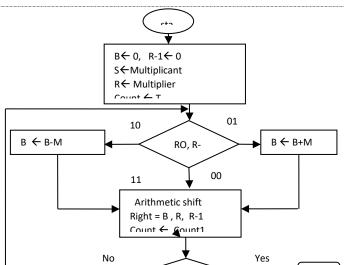

Booths multiplier was IST given by Andrew Donald booths in year 1950[16]. Booths algorithm can work low when count of partial products is high because it to perform all sums IST after that output can be generated. Function of this booths multiplier is to provide method for multiplying binary integers in signed 2's complement illustration. Hardware multiplication is same as other multiplication process like partial products are determined, shifting and summing process. Booths multiplication method is basically done by two shifting processes one is arithmetic and other one is circular. Circular shift is done by this process IST then numbers are kept in an arranged manner. After that shifting is done by two ways left circular or right circular shift operation. In left circular operation IST digit is reversely shifted to last digit and the rest bits are shifted 1 bit left. While in right shift circular shifting is done in it. The algorithm of Booth's Multiplier is given as under:

In this registers S and R are used to kept multiplicand and multipliers respectively. 1 bit register B is kept right of LSB R0 of R register. It is represented by R-1. At IST B and R-1 are set to 0. Now In this further process is done by check two bits and decision is made according to that. If both bits are same like 11 or 00 then at that time all bits of B, R, R-1 are shifted to right once. Now if combination of bits is 10 at that time subtraction process is done in which multiplicand is subtracted from B. And if combination gives 01 that time addition process is done multiplicand is added to B. In both cases the output is stored in B, also after both these addition and subtraction operation B, R, R-1 are shifted towards right. This is called arithmetic shift operation. In this sign of numbers B and R are protected. Output of multiplication comes out in B and R.

But booths multiplier takes more area for operation, power consumption is low and speed is almost same as array multiplier. Maximum number of adder cells are used by booths multiplier to provide high quality output but it has a problem that it consumes more power [17],[18]. So we prefer modified booths algorithm as compared to this so that area is reduced delay is also minimized [19].

[Hamid\* et al., 7(4): April, 2018]

ICTM Value: 3.00

Figure 8:- Design flow of Booth algorithm

#### V. RESULTS AND DISCUSSION

**Table 2: Specification of Wallace tree type.**

|                   | Wallace Tree                                                        |

|-------------------|---------------------------------------------------------------------|

| 17-bit adder      | 9                                                                   |

| 17-bit subtractor | 9                                                                   |

| 5-bit subtractor  | 1                                                                   |

| 1-bit register    | 4                                                                   |

| 33-bit register   | 1                                                                   |

| 5-bit register    | 2                                                                   |

| 1-bit 8-to-1 MIX  | 17                                                                  |

| 33-bit 2-to-1 MUX | 2                                                                   |

| Flip-Flops        | 34                                                                  |

| Delay             | 12.932ns (11.728ns logic, 1.204ns route) (58.9% logic, 41.1% route) |

Table 1: Specification of Array type.

Fnd

ISSN: 2277-9655

**CODEN: IJESS7**

**Impact Factor: 5.164**

|                              | Array16-bit                                                                                                |

|------------------------------|------------------------------------------------------------------------------------------------------------|

| Adders/Subtractors           | 15                                                                                                         |

| 32-bit adder                 | 15                                                                                                         |

| 32-bit 2-to-1<br>multiplexer | 16                                                                                                         |

| Delay:                       | 21.206 ns 206ns (Levels of Logic = 63) 21.206ns (12.743ns logic, 8.463ns route) (60.1% logic, 39.9% route) |

[Hamid\* et al., 7(4): April, 2018] ICTM Value: 3.00

**Table 3: Specifications of Vedic**

|                                 | Vedic 16 bit                                                             |

|---------------------------------|--------------------------------------------------------------------------|

| Adders/Subtractors              | 4                                                                        |

| 16-bit adder                    | 4                                                                        |

| 16-bit / 4-inputs adder<br>tree | 1                                                                        |

| 16-bit 8-to-1<br>multiplexer    | 4                                                                        |

| Delay                           | 13.701ns (6.612ns<br>logic, 7.089ns ro)<br>(43.4% logic, 56.6%<br>route) |

Table 4: Specifications of Booth's Multiplier

ISSN: 2277-9655

**CODEN: IJESS7**

**Impact Factor: 5.164**

|                           | Booth 16bit                                                                 |

|---------------------------|-----------------------------------------------------------------------------|

| 32-bit adder              | 8                                                                           |

| 3-bit comparator greater  | 7                                                                           |

| 32-bit 2-to-1 multiplexer | 7                                                                           |

| 32-bit 8-to-1 multiplexer | 8                                                                           |

| 4-bit 2-to-1 multiplexer  | 3                                                                           |

| Delay                     | 12.701ns (5.612ns<br>logic, 7.089ns route)<br>(48.3% logic, 51.7%<br>route) |

#### VI. **CONCLUSION**

On comparsion of various multipliers array multiplier has low complication and area is also low but it has difficulty that it has low speed and power utilization is higher as compared to other multipliers. On the other hand wallace tree multiplier has speed superior than array multiplier and also power utilization is also less as compared to array multiplier but area in it is huge. Vedic multiplier has lesser power consumption and complexity less it also has higher speed but it has area larger than booths multiplier. Booths multipliers has both area and power consumption less. Speed is also excellent in booth multiplier. But to make area more smaller as compared to booths and other multiplier we prefer modified booths multiplier to make more less area process.

#### VII. REFERENCES

- [1] Dong-Wook Kim, Young-Ho Seo, "A New VLSI Architecture of Parallel Multiplier-Accumulator based on Radix-2 Modified Booth Algorithm", Very Large Scale Integration (VLSI) Systems, IEEE Transactions, vol.18, pp.: 201-208, 04 Feb. 2010

- [2] M Själander, H Eriksson, P Larsson-Edefors, "An efficient twin- precision multiplier" in Proc. 22nd IEEE Int. Conf. Comput. Des, 2004, pp. 30–33

- [3] Hussain1, R. K. Sah2 and M. kumar3, "Performance Comparison of Wallace architecture" International Journal of Innovative Research in Science, Engineering and Technology (An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 1, January 2015

- [4] Kaustubh Manikrao Gaikwad and Mahesh Shrikant Chavan, "Analysis of Array Multiplier and Vedic Multiplier using Xilinx" Communications on Applied Electronics (CAE) – ISSN: 2394-4714 Foundation of Computer Science FCS, New York, USA Volume 5 - No.1, May 2016.

- [5] Savita Nair and Ajit Saraf, "A Review Paper on Comparison of Multipliers based on Performance Parameters''International Journal of Computer Applications (0975 – 8887) International Conference on Advances in Science and Technology, 2014.

- [6] Rajaram, Srinath, and K. Vanithamani. "Improvement of Wallace multipliers using parallel prefix adders. "In Signal Processing, Communication, Computing and Networking Technologies (ICSCCN), 2011International Conference on, pp. 781-784. IEEE, 2011.

- [7] Vinoth, C., VS Kanchana Bhaaskaran, B. Brindha, S.Sakthikumaran, V. Kavinilavu, B. Bhaskar, M.Kanagasabapathy, and B. Sharath. "A novel low power and high speed Wallace tree multiplier for RISC processor." In Electronics Computer Technology (ICECT), 2011 3rd International Conference on, vol. 1, pp.330-334. IEEE, 2011.

ISSN: 2277-9655 Impact Factor: 5.164 CODEN: IJESS7

- [8] Bhupender Pratap Singh, Rakesh Kumar, "Design & Implementation 8-Bit Wallace Tree Multiplier". International Journal of Advanced Research in Electrical & Electronics and Instrumentation Engineering Vol. 5, Issue 4, April 2016

- [9] Khushboo Bais, Zoonubiya Ali, "Design of a High Speed Wallace Tree Multiplier" International Journal of Engineering Sciences & Research Technology, 2016

- [10] S. Rajaram and Mrs. K. Vanithamani, "Improvement of Wallace Tree Multipliers using Parallel Prefix Adders" Proceedings of 2011 International Conference on Signal Processing, Communication, Computing and Networking Technologies (ICSCCN 2011), 2011

- [11] Yogita Bansal, Charu Madhu and Pardeep Kaur, "High Speed Vedic Multiplier Designs-A Review", Proceedings of 2014 RAECS UIET 06 08 March, 2014.

- [12] C.Sheshavali M.Tech, K.Niranjan Kumar Asst.professor, "Design and Implementation of Vedic multiplier" International Journal of Engineering Research and Development, Volume 8, Issue 6 September, 2013.

- [13] Akanksha Kant, Shobha Sharma, "Applications of Vedic Multiplier Designs-A Review "978-1-4673-7231-2/15, IEEE, 2015.

- [14] Harpreet Singh Dhillon and Abhijit Mitra "A Digital Multiplier Architecture using Urdhava Tiryakbhyam Sutra of Vedic Mathematics" IEEE conference Proceedings, 2008.

- [15] Pramod S. Aswale, Priyanka Nirgude, Bhakti Patil, Rohini Chaudhari," Implementation of multipliers using vedic mathematics" 1<sup>st</sup>, 2<sup>nd</sup> April 2017

- [16] Deepali Chandell, Gagan Kumawat, Pranay Lahoty, Vidhi Vart Chandrodaya, Shailendra Sharma "Booth Multiplier: Ease of multiplication" in International Journal of Emerging Technology and Advanced Engineering, Volume 3, Issue 3, March 2013).

- [17] Tam Anh Chu, "Booth Multiplier with Low Power High Performance Input Circuitry", US Patent, 6.393.454 B1, May 21, 2002.

- [18] Sumit Vaidya and Deepak Dandekar "Delay-power performance Comparison of multipliers in VLSI Circuit design" in International Journal of Computer Networks & Communications (IJCNC), Vol.2, No.4, July 2010.

- [19] Neha Goyal, Khushboo Gupta & Renu Singla, "study of combinational and booths multiplier" 'International Journal of Scientific and Research Publications, Volume 4, Issue 5, May 2014.

#### **CITE AN ARTICLE**

Hamid, A. B., Beigh, N. T., & Ganiee, S. A. (n.d.). COMPARATIVE ANALYSIS OF BOOTH'S MULTIPLIER IN TERMS OF DESIGN PARAMETER. *INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY*, 7(4), 638-645.